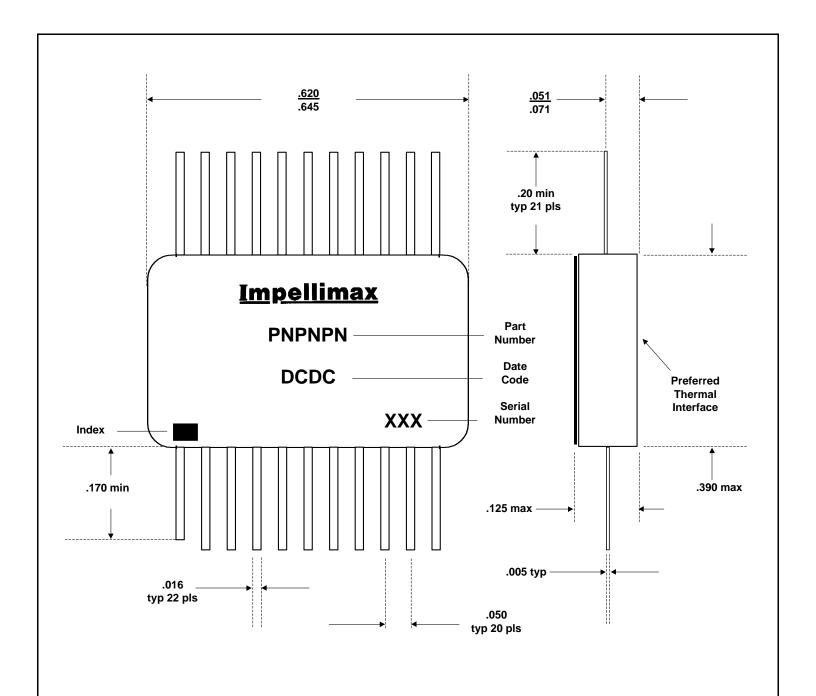

| Tolerances Except as Noted .x = +/05 .xx = +/01 .xxx = +/005 Dimensions in inches | Revisions |          |         |      | <u>lm</u> p <u>ellimax</u> |                    |              |

|-----------------------------------------------------------------------------------|-----------|----------|---------|------|----------------------------|--------------------|--------------|

|                                                                                   | A         | ECO 2057 | 6/28/00 | P.C. | OUTLINE                    |                    |              |

|                                                                                   |           |          |         |      |                            |                    | Sheet 1 of 2 |

| Information herein is believed accurate. Suitability not                          |           |          |         |      | Drawn By:<br>P. C.         | Date: 3/1/90       | Drawing #    |

| guaranteed.                                                                       |           |          |         |      | DRF:                       | Approved:<br>P. C. | GS4-50       |

| PIN | CONNECTION   | PIN | CONNECTION |

|-----|--------------|-----|------------|

| 1   | -5 V to -18V | 22  | NC         |

| 2   | NC           | 21  | Out 1 NI   |

| 3   | Rset         | 20  | Out 1 Inv  |

| 4   | Ground       | 19  | Out 2 NI   |

| 5   | In 1         | 18  | Out 2 Inv  |

| 6   | ln 2         | 17  | Out 3 NI   |

| 7   | In 3         | 16  | Out 3 Inv  |

| 8   | In 4         | 15  | Out 4 NI   |

| 9   | NC           | 14  | Out 4 Inv  |

| 10  | NC           | 13  | NC         |

| 11  | +5V          | 12  | -V Int     |

## Notes:

- 1) Channels are independent and TTL compatible. Logic "0" is defined as 0.8 V max, logic "1" is 1.4 to 5 V max. Logic low TTL current is 0.5 mA max.

- 2) Noninverting outputs are at ground for TTL hi, and inverting outputs are at negative.

- 3) Switching speed is 30 nsec typical.

- 4) Unit contains internal .01 uF bypass capacitors.

- 5) Connect resistor (in the range of 2K to 10K) from Rset (pin 3) to -V (pin 1) to set negative output voltage. Alternatively, apply -5 to -8 V directly to V Int (pin 12).

|   | Tolerances<br>Except as Noted<br>x = +l - 0.05<br>.xx = +l - 0.01<br>.xxx = +l - 0.05<br>Dimensions<br>in inches | Revisions |          |         |      | <u>lmpellimax</u>  |                    |              |

|---|------------------------------------------------------------------------------------------------------------------|-----------|----------|---------|------|--------------------|--------------------|--------------|

|   |                                                                                                                  | Α         | ECO 2057 | 6/28/00 | P.C. | OUTLINE            |                    |              |

|   |                                                                                                                  |           |          |         |      |                    |                    |              |

|   |                                                                                                                  |           |          |         |      |                    |                    | Sheet 2 of 2 |

| • | Information herein is believed accurate. Suitability not                                                         |           |          |         |      | Drawn By:<br>P. C. | Date: 3/1/90       | Drawing #    |

|   | guaranteed.                                                                                                      |           |          |         |      | DRF:               | Approved:<br>P. C. | GS4-50       |